# Digital Logic and Computer Organization

Combinational Logic - Analysis and Design

# **Combinational Circuit**

- A circuit consists of an inter-connection of logic gates.

- A logic circuit is combinational if its output(s) are a function of only the present inputs at any time.

- The inputs to a circuit can be viewed as binary variables from an external source.

- The outputs of a circuit are variables produced by the circuit based on the input signals and go to external destinations.

- For n input variables, there are 2<sup>n</sup> possible combination of the binary inputs.

- For each distinct input combination, there is one value for each output variable.

### Analysis of Combinational Circuits

- How to make sure the circuit to be analyzed is combinational? In the schematic, there is no feedback paths or memory elements.

- Analyze by establishing a truth table: for each input combination, trace the schematic to establish its output.

- Literal analysis

- Use meaningful symbols to name the output of each gate in the circuit;

- Starting from the gates whose inputs are circuit inputs, find the Boolean functions for these gates;

- For those gates whose inputs include the output of other gates whose functions are already established, find the Boolean functions for these gates;

- Repeat the previous step until the Boolean function of the circuit's output is found.

# Design Procedure

- From the specifications of the circuit, determine the required number of inputs and outputs and assign a symbol to each; (determine the interface of the circuit;)

- Derive the truth table that defines the required relationship between inputs and outputs; (determine the behaviour of the circuit;)

- Obtain the simplified Boolean function for each output as a function of the input variables; (determine the functionality of the circuit;)

- Draw the logic schematic; (determine the structure of the circuit;)

- Verify the correctness of the design by building a prototype or by simulation.

### Design Examples/ Applications

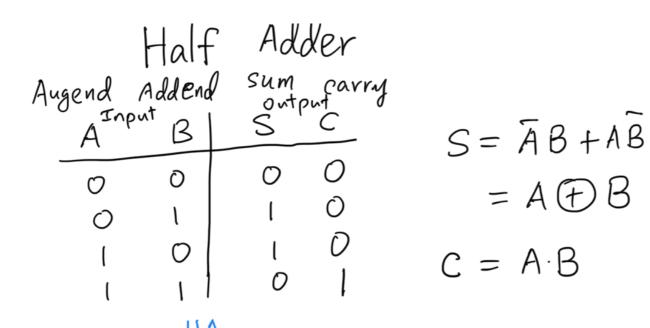

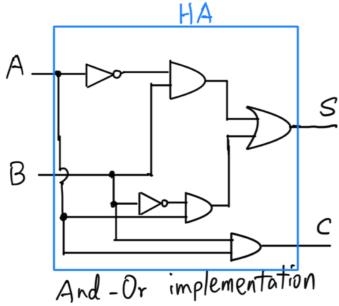

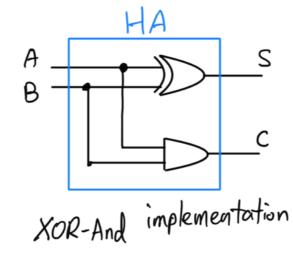

Half Adders

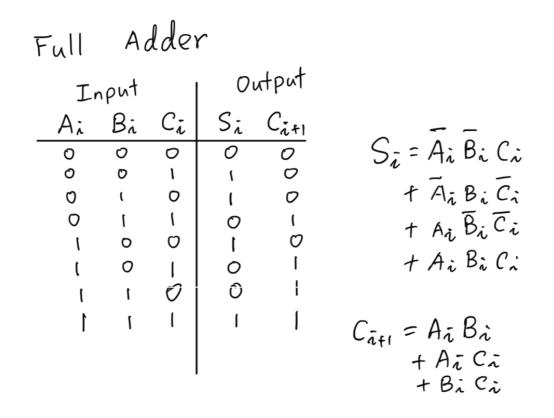

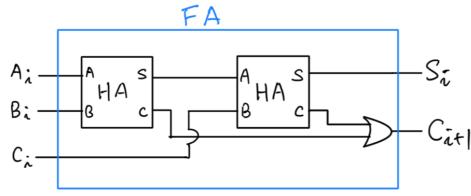

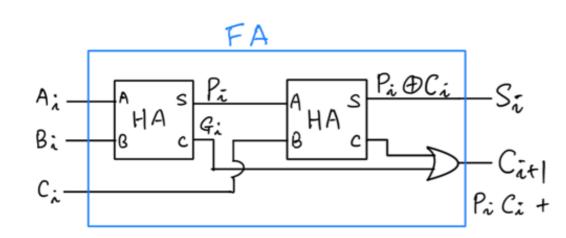

## Full Adder

• Full Adder: Sum-of-Product; 2 Half Adders and an OR

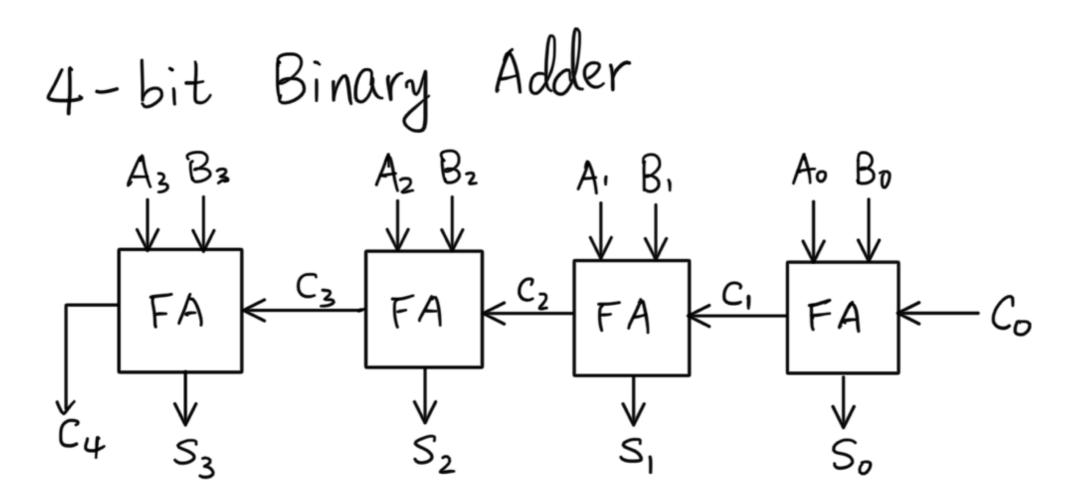

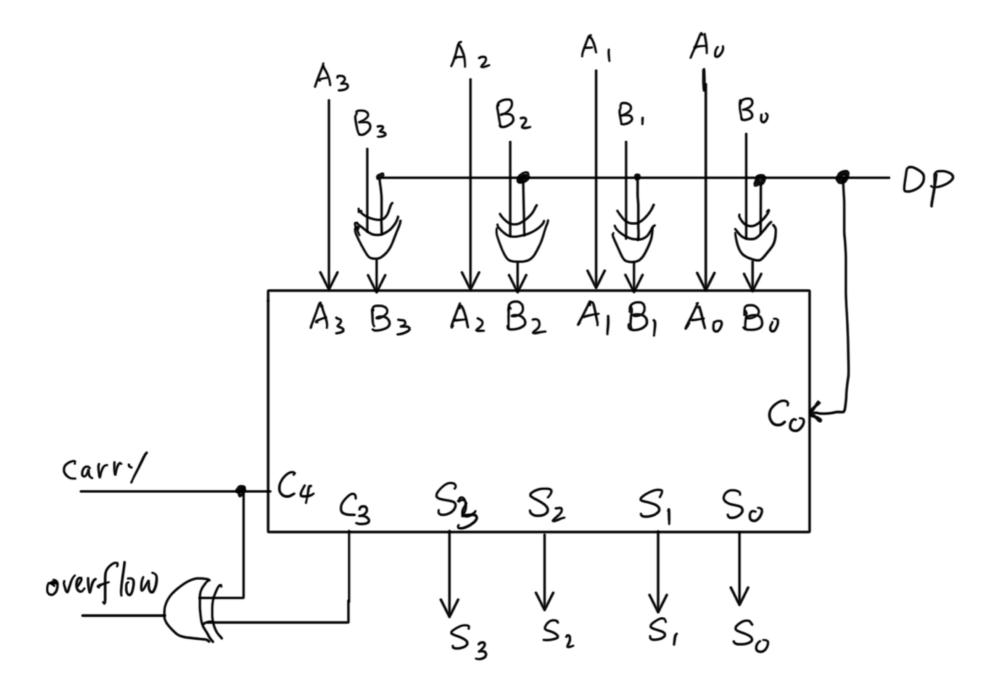

# **Binary Adder**

Binary Adder: Multi-bit ripple carry Adder

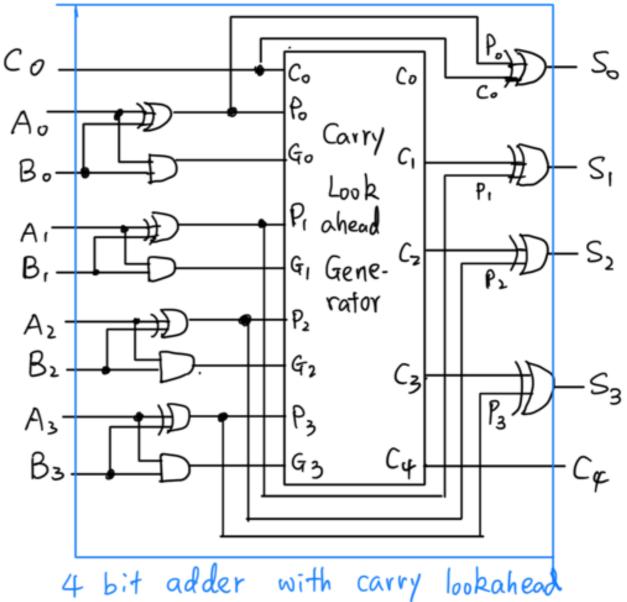

# **Binary Adder**

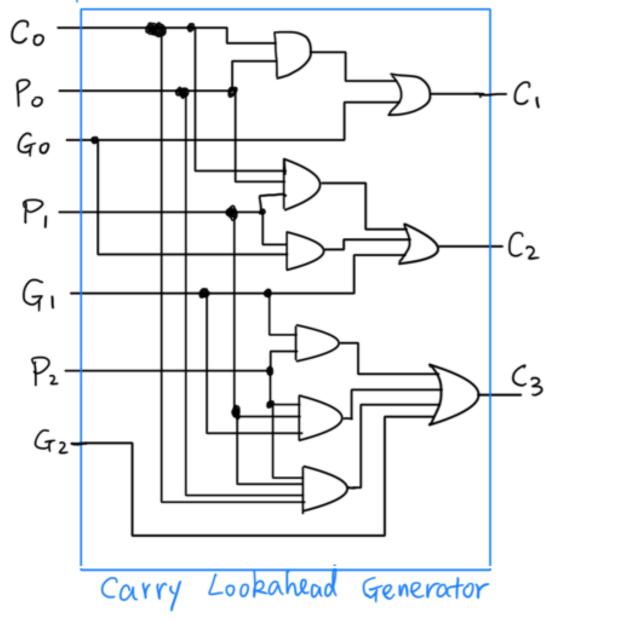

- Issue: Carry propagation causing delays

- Solution: Carry lookahead

#### Binary Adder with Lookahead

## **Binary Subtractor**

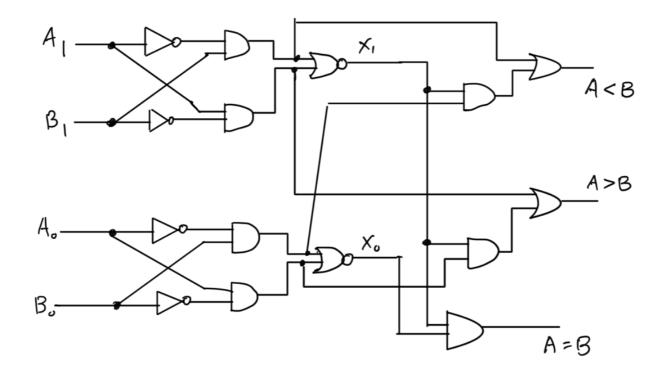

## Magnitude Comparator

$$X_{i} = A_{i}B_{i} + \overline{A_{i}B_{i}} \quad \text{for } i = 0, 1, 2, 3$$

$$F_{A=B} = X_{3} \cdot X_{2} \cdot X_{1} \cdot X_{0}$$

$$F_{(A>B)} = A_{3}\overline{B}_{3} + X_{3}\overline{A}_{2}\overline{B}_{2} + X_{3}X_{2}\overline{A}_{1}\overline{B}_{1} + X_{3}X_{2}X_{1}\overline{A}_{0}\overline{B}_{0}$$

$$F_{(A$$

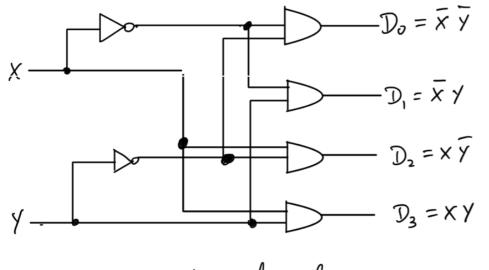

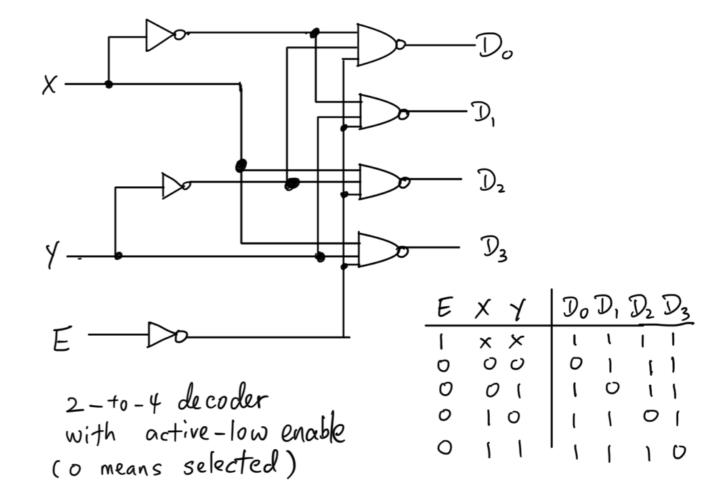

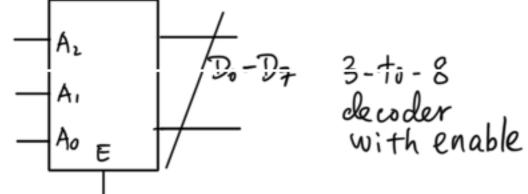

### Decoder

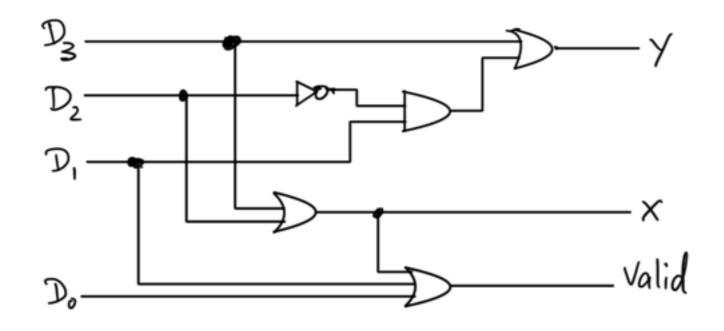

#### **Encoder & Priority Encoder**

| II                | iput             |                |                   | 0 | v | tput |                 | I                 | npn                  |

|-------------------|------------------|----------------|-------------------|---|---|------|-----------------|-------------------|----------------------|

| $\mathcal{D}_{o}$ | $\mathbb{D}_{1}$ | $\mathbb{D}_2$ | $\mathcal{D}_{3}$ | > | < | У    | $X = D_2 + D_3$ | $\mathcal{D}_{0}$ | $\mathcal{D}$        |

| ۱                 | 0                | 0              | 0                 |   | 0 | 0    | $y = D_1 + D_3$ | Ð                 | Ô                    |

| 0                 | 1                | 0              | O                 | ( | С | I    | 1- 1,1 23       | 1                 | C                    |

| Ø                 | 0                | 1              | 0                 |   | ι | 0    |                 | ~                 | ,                    |

| 0                 | 0                | D              | ۱                 |   | 1 | l    |                 | $\sim$            | I                    |

|                   |                  |                |                   |   |   |      |                 | ×                 | <ul> <li></li> </ul> |

| I                | npnt              |                  | output           |   |  |   |   |       |

|------------------|-------------------|------------------|------------------|---|--|---|---|-------|

| $\mathbb{D}_{0}$ | $\mathcal{D}_{1}$ | $\mathbb{D}_{2}$ | $\mathbb{D}_{3}$ |   |  | Х | Y | Valid |

| Ð                | ð                 | 0                | 0                |   |  | Х | Х | 0     |

| l                | 0                 | Ο                | 0                |   |  | D | O | I     |

| ×                | 1                 | 0                | 0                | İ |  | D | ۱ | 1     |

| Х                | $\times$          | 1                | 0                |   |  | ι | 0 | t     |

| Х                | Х                 | 1                | ۱                | I |  | ١ | ۱ | l     |

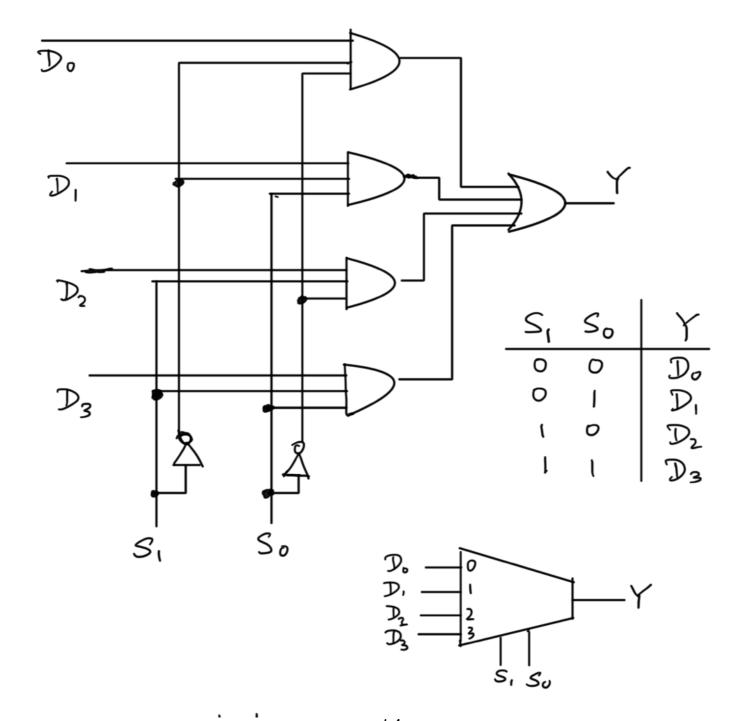

## Multiplexer

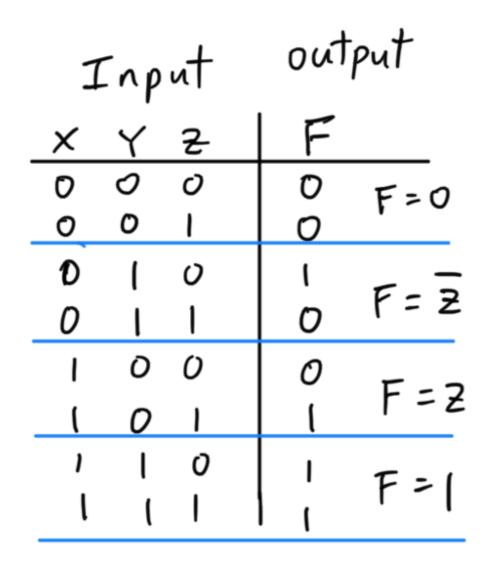

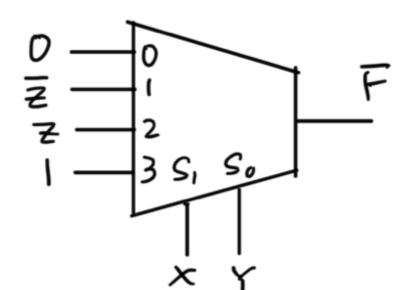

### Implement Function using Multiplexer

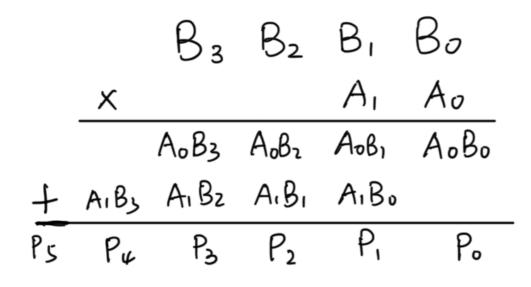

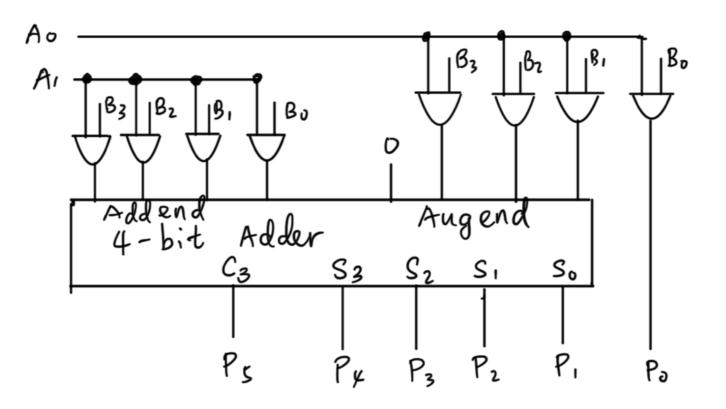

# **Binary Multiplier**