## Digital Logic and Computer Organization

Sequential Logic — Latches

# Sequential Logic

- a logic circuit whose output depends on the present value of its input signals and on the sequence of past inputs.

- Brutally simplified view: a logic circuit that has memory elements.

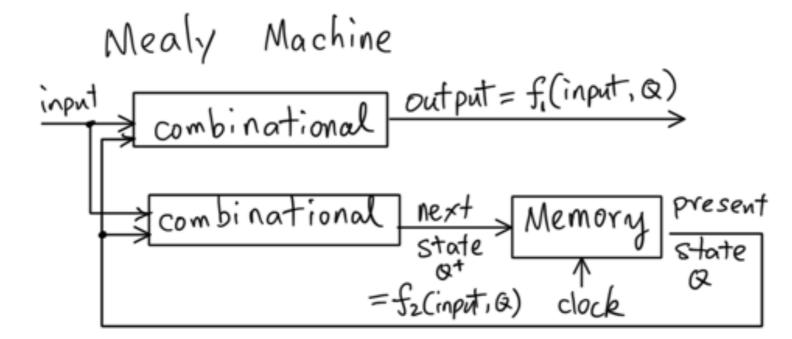

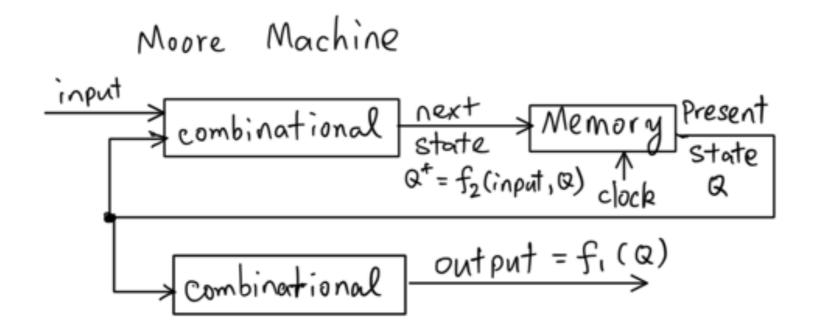

## Mealy vs Moore Machine

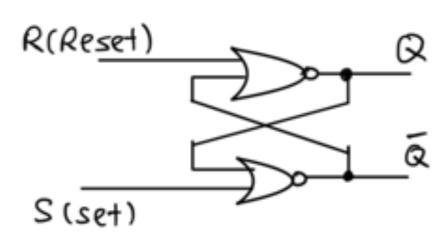

## **SR Latch with NOR**

| characteristic<br>table |   |    |                    | Excitation<br>table |    |     |   |

|-------------------------|---|----|--------------------|---------------------|----|-----|---|

| 5                       | R | Qt |                    | Q                   | Qf | S   | R |

| Ø                       | 0 | Q  | unchanged<br>reset | 0                   | 0  | 0   | × |

| 0                       | ١ | 0  | reset              | 0                   | ι  | l ( | 0 |

| ۱.                      | 0 | 1  | set                | ١                   | 0  | 0   | 1 |

| 1                       | 1 |    | invalid            |                     |    |     | ċ |

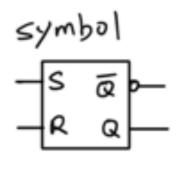

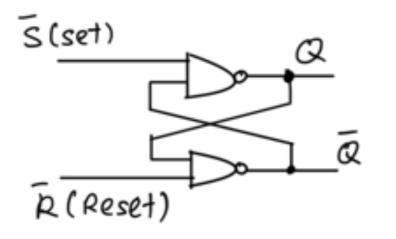

## SR Latch with NAND

| Ś | R | Qt    | āt    |

|---|---|-------|-------|

| 0 | ١ | 1     | 0     |

| ۱ | D | 0     | ١     |

| ١ | I | Q     | ā     |

| D | O | Junde | fined |

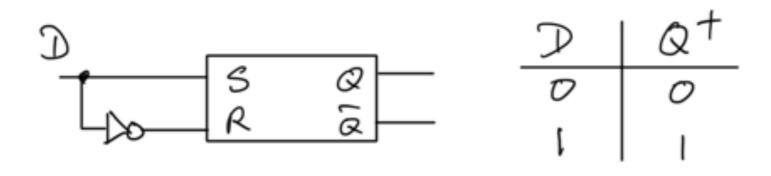

## **D** Latch

$Q^+ = D$

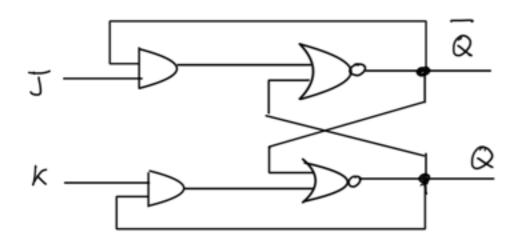

#### JK Latch

$$\begin{array}{c|c|c} J & K & Q^{\dagger} \\ \hline 0 & 0 & Q \\ 0 & I & 0 \\ I & 0 & I \\ 1 & 1 & Q \end{array}$$

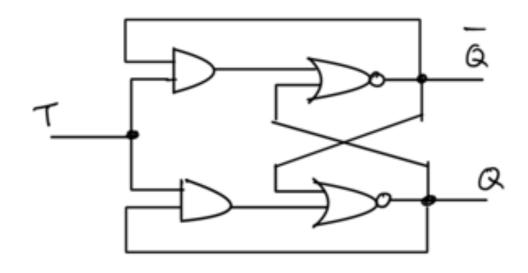

### T Latch

when

$$T = 1$$

output oscillates

$Q^{+} = TQ + TQ$

$= T \oplus Q$