# CSCI 355 Digital Logic and Computer Organization Laboratory Manual

Dr. Peter Walsh

Department of Computing Science Vancouver Island University Nanaimo, B.C., V9R 5S5, Canada

Version 0.7 Fall 2013

## 1. Preamble

CSCI 355 is concerned with the analysis and design of digital circuits. Two methods of design verification are employed. First, a software model of the design is developed and tested using the hardware description language Verilog. Then, the design is physically realized and tested in the laboratory.

Design modeling using Verilog is discussed in the lecture portion of this course. Models are developed for simulation and designs are realized on a breadboard using standard ICs (integrated circuits).

Breadboarding is overviewed in section 2 and section 3 discusses experiment deliverables. The remainder of the manual contains a series of laboratory tasks (experiments) and data sheet appendices.

## 2. Breadboarding

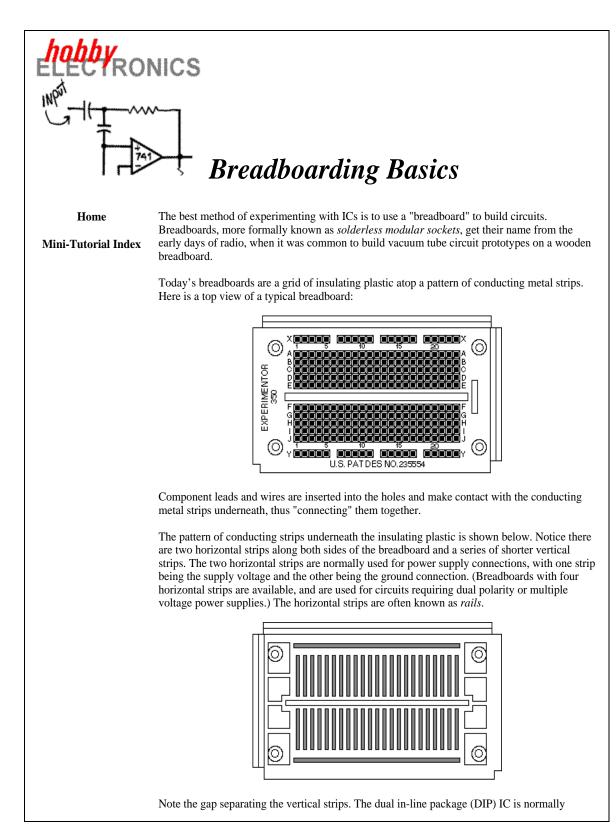

During breadboarding, you will plug the necessary ICs into the breadboard, cut wires of proper length, and connect the ICs on the breadboard using the wires according to your design specification (schematic). At the end of this section, a tutorial from Hobby Electronics introduces basic breadboarding (http://www.hobby-electronics.com/MiniTutorialIndex.htm). The following descriptions assume you have read and understood the tutorial.

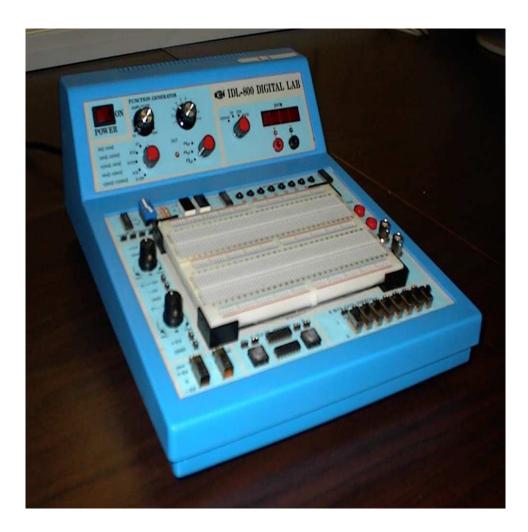

#### **IDL-800** Digital Circuit Evaluator

Our laboratory is equipped with IDL-800 digital circuit evaluators. The IDL-800 has 19 different basic components. Initially, you will be concerned with the following 6 components:

1 power switch with indicator

- 2 pulse switches

- 3 level switches

- 4 removable solderless breadboard

- 5 fixed DC +5volts and ground

- 6 leds (lamps)

IDL-800 Digital Circuit Evaluator

#### Wiring Technique

It is important to develop good wiring technique when realizing your designs on a breadboard. Good wiring technique will help both the student and the instructor test and debug your circuit realization. The following convention must be adhered to:

- Power to the IDL-800 should be off before you insert or remove wires or ICs from the unit.

- Insert your required ICs into the breadboard gap as described in the tutorial. Note that ICs have a notch that is used as an alignment reference. ICs have legs or pins that are the input/output interface to the circuits on the chip. The legs bend easily, you may have to align them (straighten them) before inserting the IC in the breadboard gap. Make sure adjacent IC legs are inserted into adjacent breadboard pin-holes. To achieve correct IC orientation, the two rows of IC legs must straddle the breadboard gap and the IC notch must be on the left hand side of the IC.

- To remove an IC from the breadboard, slide an IC chip extractor under the body of the chip and lift gently (a pencil will work if you dont have an extractor to hand).

- Cut wires to the appropriate length. Route wires around, not over ICs. Whenever possible, make manhatten (90 degree) wiring turns along unoccupied sections of the breadboard. Colour code your wires. Use red for +5volts, black for ground, green for data signals and blue for control signals. Use the rails to supply +5 and ground signals to the ICs.

The following wiring sequence is strongly recommended:

- wire the +5volts and ground rails

- wire the +5volts and ground signals (from the rails to the ICs)

- wire data signals

- wire control signals

One final note, on occasion, you may end up using an IC that is faulty. Consequently, it is strongly recommended that you verify the operation of each IC in isolation BEFORE you wire-up your circuit.

Breadboarding Basics: Page 1 of 2

the opposite side.

| row | of pii | ns is c | on |

|-----|--------|---------|----|

|     |        |         |    |

Breadboards come in a variety of sizes, and are usually measured in terms of the number of connection or "tie points" provided. Some breadboards come with binding posts for connecting a power supply; deluxe models have power supplies built in and with additional supports for potentiometers, LEDs, and meters.

placed across this gap. One row of pins is one side of the gap, and the other

Copyright 1998 © by LLH Technology Publishing LLC

Breadboarding Basics: Page 2 of 2

## 3. Experiment Deliverables and Evaluation

The remainder of the manual contains a series of laboratory tasks (experiments). Each experiment has a pre-lab component and an in-lab component. In the pre-lab component, you develop solution(s) to the laboratory task(s) and verify your design(s) by building and testing Verilog model(s). All files relating to laboratory work will be made available through git.

In the in-lab component, your task is to realize your circuit design(s), verify them and record any relevant observations you made during the in-lab period.

Pre-lab Verilog code is due before 12:00 noon on the day BEFORE your scheduled in-lab time. If your model(s) fail any of the supplied test cases (in the testbench(s)) then you will not be allowed to proceed to the in-lab component. You will receive no credit for the experiment.

You must complete a experiment report for each laboratory task. Your report must pass the following basic acceptance tests:

- 1 Lab reports must consist of letter-sized pages.

- 2 All pages in your Lab report must be stapled together (top left-hand corner).

- 3 All pages in the lab report must be numbered in the top right-hand corner (as exemplified in the model solution for Lab0).

- 4 All lab report deliverables must be labelled, complete and presented in-order. (again, see model solution for Lab0). Appendices must be included at the end of the report and referenced in the appropriate deliverable.

- 5 All lab report deliverables must be accurate with no intent to fake results.

- 6 With regard to modifications/additions to computer code work-products, code must run/simulate without warnings or crashes and students must enter their name in the "Revision List" for that work-product. Verilog/Cew code indenting must conform to the style exemplified in the TTL models. Verilog/Cew code run-time/simulation-time behaviour must be to specification (typically, make ttl must indicate no errors).

- 7 All lab work must be completed on an individual basis (unless otherwise stated, group answers constitute plagiarism).

If your report fails any of the basic acceptance tests then you will receive no credit for the experiment

The lab report is due at the beginning of your in-lab time; all report deliverables must be in place with the exception of deliverables that are due by the end of your in-lab time. Once you have constructed and verified the behaviour of your circuit, sign your report to indicate your circuit behaves as specified. Then, ask your instructor to check your work. If either your design or implementation if found to be flawed, you will receive no credit for the physical realization component of the experiment. Submit the complete report to your instructor at the end of the in-lab time.

Each Lab is graded out of 10 points. The breakdown is as follows:

- 1 points: report presentation

- 5 points: report deliverables

- 4 points: physical circuit behaviour

A sample report follows the statement of Lab0. You need not word-process your reports

but hand drawn figures and writing must be clear and legible.

The exact wiring connections for your circuit must be detailed in pin-out sheets. You must complete at least one pin-out sheet for each IC employed in your physical circuit. For a given IC, each row in its pin-out sheet details a wire connecting one of its pins to another pin on the same IC or to a pin on a different IC. Consider wire X. Let the the source and destination of wire X be called A and B. When the pin-out is done correctly, you will find that X's connection details are listed at least twice; first detailing the connection from A to B and then detailing the connection from B to A. At the end of a pin-out sheet, you may repeat *significant* connections such as connections to switches and leds. You must use the pin-out sheet template for all pin-outs.

## Experiment 0

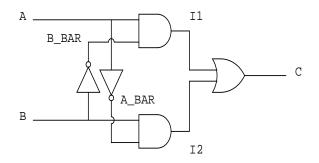

With reference to the combinational system specified in the following logic schematic:

Task (T1): Perform symbolic analysis.

Deliverable (D1): Network expression specifying C in terms of A and B.

Task (T2): Perform literal analysis.

Deliverable (D2): Truth table with one output column for each of A\_BAR, B\_BAR, I1, I2 and C.

**Task (T3):** Develop a sinthesizable structural Verilog model of the combinational system using the Verilog models for the TTL ICs SN7404, SN7408 and SN7432.

Deliverable (D3): Electronic submission of source code (make submit).

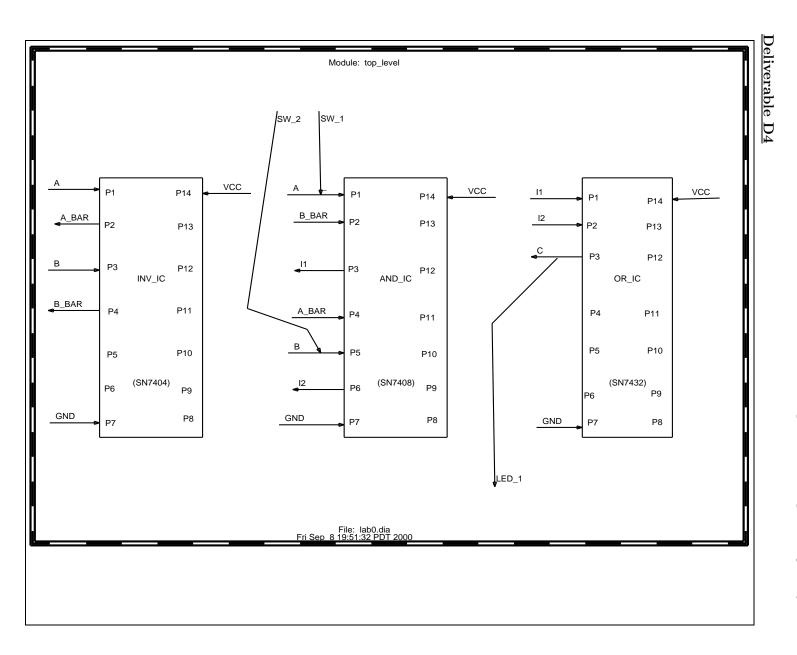

**Task (T4):** Map your Verilog model to a TTL-based physical design for the combinational system.

Deliverable (D4): IC logic schematic.

Task (T5): Specify IC interconnections.

**Deliverable (D5):** One completed pin-out sheet (at least) for each IC employed in your physical design.

**Task (T6):** In the laboratory, wire-up your physical design, verify its behaviour and sign-off on the design/implementation.

**Deliverable (D6):** A physical bread-board realization of the combinational system that behaves to specification. Details of the circuit-verification process. Student signature indicating that the circuit behaves as specified.

Task (T7): Document any relevant results, explanations or comments.

**Deliverable (D7):** A section in your report entitled Results/Explanations/Comments in which you have detailed any relevant results, explanations or comments.

## NOTES

Experiment 0 Report: Page 1 of 6

## $\mathrm{CSCI}\ 355$

## Experiment 0 Report

## Peter Walsh (Lab Section F0001)

<u>Deliverable D1</u>

$$C=\mathtt{A}\overline{\mathtt{B}}+\overline{\mathtt{A}}\mathtt{B}$$

## Deliverable D2

| A | В | A_BAR | B_BAR | I1 | 12 | С |

|---|---|-------|-------|----|----|---|

| 0 | 0 | 1     | 1     | 0  | 0  | 0 |

| 0 | 1 | 1     | 0     | 0  | 1  | 1 |

| 1 | 0 | 0     | 1     | 1  | 0  | 1 |

| 1 | 1 | 0     | 0     | 0  | 0  | 0 |

### **Deliverable D3**

Submitted electronically through make submit.

14

## Deliverable D5

CSCI 355 Laboratory Pin-Out Sheet

| STUDENT NAME      | Peter W       |

|-------------------|---------------|

| EXPERIMENT NUMBER | <u>0</u>      |

| IC NUMBER         | <u>SN7432</u> |

IC INSTANCE NAME OR\_IC

| Source     |            | Source Destination |            |

|------------|------------|--------------------|------------|

| Pin Number | Alias Name | Pin Number         | Alias Name |

|            | (optional) |                    | (optional) |

|            |            |                    |            |

| P1         | A1         | AND_IC.P3          | Y1         |

| P2         | B1         | AND_IC.P6          | Y2         |

| P3         | Y1         | LED_1              |            |

| P7         | GND        | +0V                |            |

| P14        | VCC        | +5V                |            |

|            |            |                    |            |

| LED_1      |            | OR_IC.P3           | Y1         |

|            |            |                    |            |

|            |            |                    |            |

|            |            |                    |            |

|            |            |                    |            |

|            |            |                    |            |

Page\_\_3\_\_\_0f\_\_6\_\_\_\_

# CSCI 355 Laboratory Pin-Out Sheet

| STUDENT NAME      | $\underline{\text{Peter }W}$ |

|-------------------|------------------------------|

| EXPERIMENT NUMBER | <u>0</u>                     |

| IC NUMBER         | <u>SN7408</u>                |

| IC INSTANCE NAME  | AND_IC                       |

| Source     |            | Destination |            |  |

|------------|------------|-------------|------------|--|

| Pin Number | Alias Name | Pin Number  | Alias Name |  |

|            | (optional) |             | (optional) |  |

|            |            |             |            |  |

| P1         | A1         | INV_IC.P1   | A1         |  |

|            |            | SW_1        |            |  |

| P2         | B1         | INV_IC.P4   | Y2         |  |

| P3         | Y1         | OR_IC.P1    | A1         |  |

| P4         | A2         | INV_IC.P2   | Y1         |  |

| P5         | B2         | INV_IC.P3   | A2         |  |

|            |            | SW_2        |            |  |

| P6         | Y2         | OR_IC.P2    | B1         |  |

| P7         | GND        | +0V         |            |  |

| P14        | VCC        | +5V         |            |  |

|            |            |             |            |  |

| SW_1       |            | AND_IC.P1   | A1         |  |

| SW_2       |            | AND_IC.P5   | B2         |  |

Page\_\_4\_\_\_0f\_\_6\_\_\_\_

# CSCI 355 Laboratory Pin-Out Sheet

| STUDENT NAME      | Peter W       |

|-------------------|---------------|

| EXPERIMENT NUMBER | <u>0</u>      |

| IC NUMBER         | <u>SN7404</u> |

| IC INSTANCE NAME  | INV_IC        |

SourceDestinationPin Number Alias Name Pin Number Alias Name (optional) (optional) A1P1 $\rm AND\_IC.P1$ A1P2Y1 $AND\_IC.P4$ A2 $\mathbf{P3}$ A2AND\_IC.P5 B2Y2 $\mathbf{P4}$  $AND\_IC.P2$ B1 $\mathbf{P7}$ GND +0V $\mathbf{VCC}$ P14 +5V

Page\_\_5\_\_\_0f\_\_6\_\_\_\_

Experiment 0 Report: Page 6 of 6

#### **Deliverable D6**

Exhaustive testing (all 4 input test patterns) was employed. The physical system (bread-board) behaved as specified. Signature: Peter W

### **Deliverable D7**

Results/Explanations/Comments:

Nothing further to report.

####

Photographs of physical realizations of the circuit from Experiment 0 can be accessed from the csci 355 course web page.

## Experiment 1

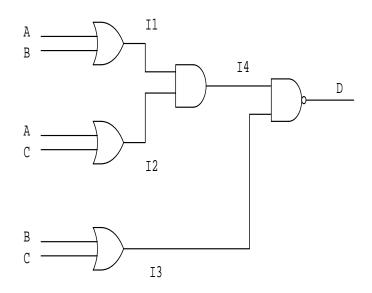

With reference to the combinational system specified in the following logic schematic:

Task (T1): Perform symbolic analysis.

Deliverable (D1): Network expression specifying D in terms of A, B and C.

Task (T2): Perform literal analysis.

Deliverable (D2): Truth table with one output column for each of I1, I2, I3, I4 and D.

**Task (T3):** Develop a structural Verilog model of the combinational system using the Verilog models for the TTL ICs SN7432, SN7408 and SN7400.

Deliverable (D3): Electronic submission of source code (make submit).

**Task (T4):** Map your Verilog model to a TTL-based physical design for the combinational system.

Deliverable (D4): IC logic schematic.

Task (T5): Specify IC interconnections.

**Deliverable (D5):** One completed pin-out sheet (at least) for each IC employed in your physical design.

**Task (T6):** In the laboratory, wire-up your physical design, verify its behaviour and sign-off on the design/implementation.

**Deliverable (D6):** A physical realization of the combinational system that behaves to specification. Details of the circuit-verification process. Student signature indicating that the circuit behaves as specified.

Task (T7): Document any relevant results, explanations or comments.

**Deliverable (D7):** A section in your report entitled Results/Explanations/Comments in which you have detailed any relevant results, explanations or comments.

# NOTES